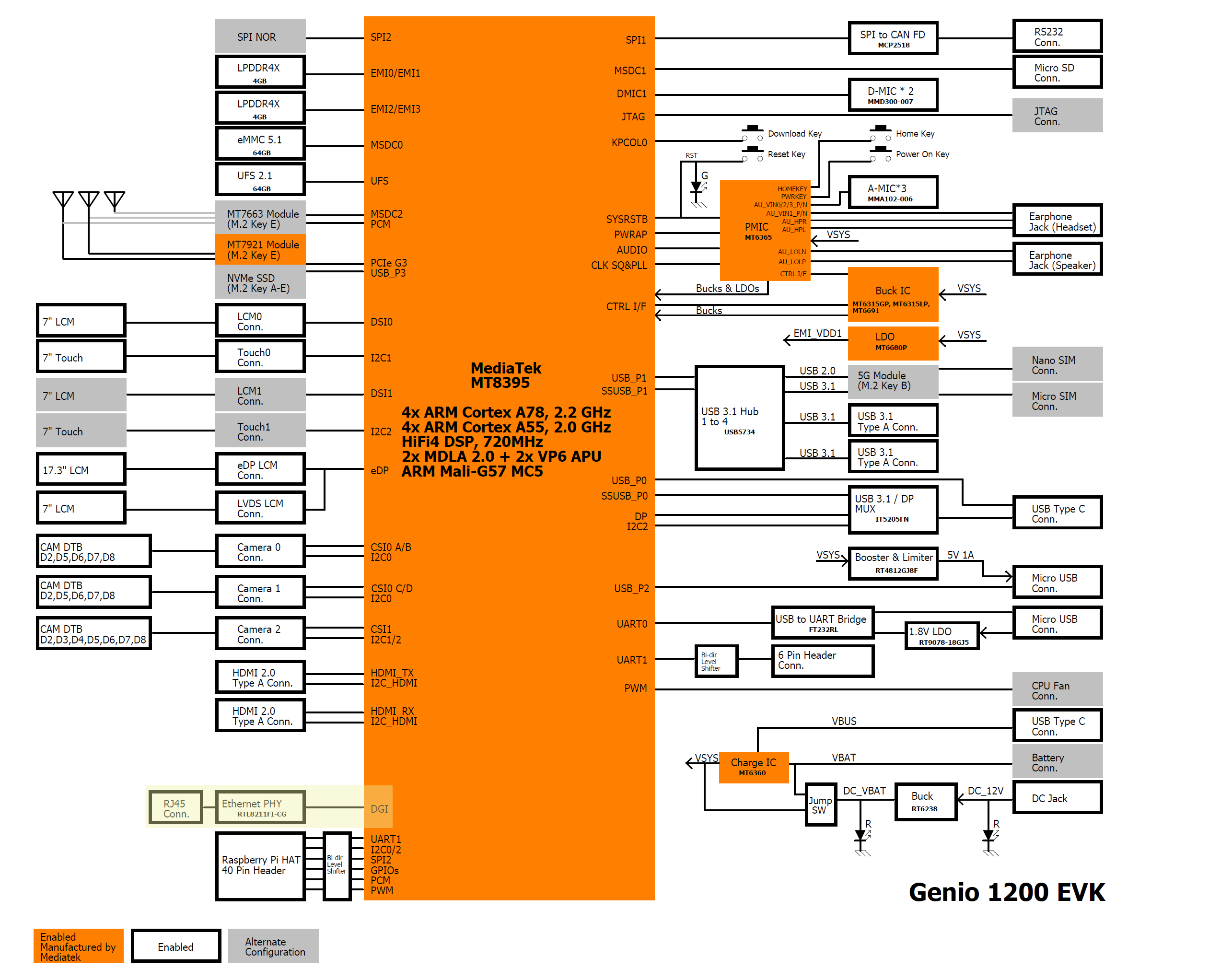

Genio 1200-EVK

This chapter describes platform-dependent information and instructions. For example, you will get different benchmark results on different platforms.

For general usage of Ethernet, such as command to configure Dynamic Host Configuration Protocol (DHCP) or static IP and so on, please refer to Ethernet chapter.

Note

This chapter presents command operations and test results from IoT Yocto v23.0 and Genio 1200-EVK.

Important

Genio 1200 Evaluation Kit (EVK) boards do not ship with pre-allocated Media Access Control (MAC) addresses.

Instead, the system generates and stores a random MAC address after flashing the image. Please do not use it for production purposes.

Ethernet Port on Genio 1200-EVK

The Ethernet interface support gigabit speed on Genio 1200-EVK:

Ethernet Port on Genio 1200-EVK

Enable Ethernet Port on Genio 1200-EVK

The system enables Ethernet by default. You can check kernel configurations with the following command: zcat /proc/config.gz | grep DWMAC.

You will find the system has enabled the following settings.

zcat /proc/config.gz | grep DWMAC

CONFIG_DWMAC_GENERIC=y

CONFIG_DWMAC_MEDIATEK=y

You can also check kernel log with the following command: dmesg | grep dwmac to confirm it has been probed properly.

dmesg | grep dwmac

dwmac-mediatek 11021000.ethernet: IRQ eth_wake_irq not found

dwmac-mediatek 11021000.ethernet: IRQ eth_lpi not found

dwmac-mediatek 11021000.ethernet: Cannot get CSR clock

dwmac-mediatek 11021000.ethernet: User ID: 0x11, Synopsys ID: 0x51

dwmac-mediatek 11021000.ethernet: DWMAC4/5

dwmac-mediatek 11021000.ethernet: DMA HW capability register supported

dwmac-mediatek 11021000.ethernet: RX Checksum Offload Engine supported

dwmac-mediatek 11021000.ethernet: TX Checksum insertion supported

dwmac-mediatek 11021000.ethernet: Wake-Up On Lan supported

dwmac-mediatek 11021000.ethernet: TSO supported

dwmac-mediatek 11021000.ethernet: device MAC address 0e:92:2b:8c:c6:fa

dwmac-mediatek 11021000.ethernet: Enabled L3L4 Flow TC (entries=4)

dwmac-mediatek 11021000.ethernet: Enabled RFS Flow TC (entries=10)

dwmac-mediatek 11021000.ethernet: SPH feature enabled

dwmac-mediatek 11021000.ethernet: Using 35/40 bits DMA host/device width

dwmac-mediatek 11021000.ethernet end0: renamed from eth0

dwmac-mediatek 11021000.ethernet end0: Register MEM_TYPE_PAGE_POOL RxQ-0

dwmac-mediatek 11021000.ethernet end0: Register MEM_TYPE_PAGE_POOL RxQ-1

dwmac-mediatek 11021000.ethernet end0: Register MEM_TYPE_PAGE_POOL RxQ-2

dwmac-mediatek 11021000.ethernet end0: Register MEM_TYPE_PAGE_POOL RxQ-3

dwmac-mediatek 11021000.ethernet end0: PHY [stmmac-0:01] driver [RTL8211F Gigabit Ethernet] (irq=POLL)

dwmac4: Master AXI performs any burst length

dwmac-mediatek 11021000.ethernet end0: Enabling Safety Features

dwmac-mediatek 11021000.ethernet end0: IEEE 1588-2008 Advanced Timestamp supported

dwmac-mediatek 11021000.ethernet end0: registered PTP clock

dwmac-mediatek 11021000.ethernet end0: FPE workqueue start

dwmac-mediatek 11021000.ethernet end0: configuring for phy/rgmii-rxid link mode